2022 Solution 02

2022 Solution 02

Isaac P Abraham

2022 Feb 23

2022 Feb 23

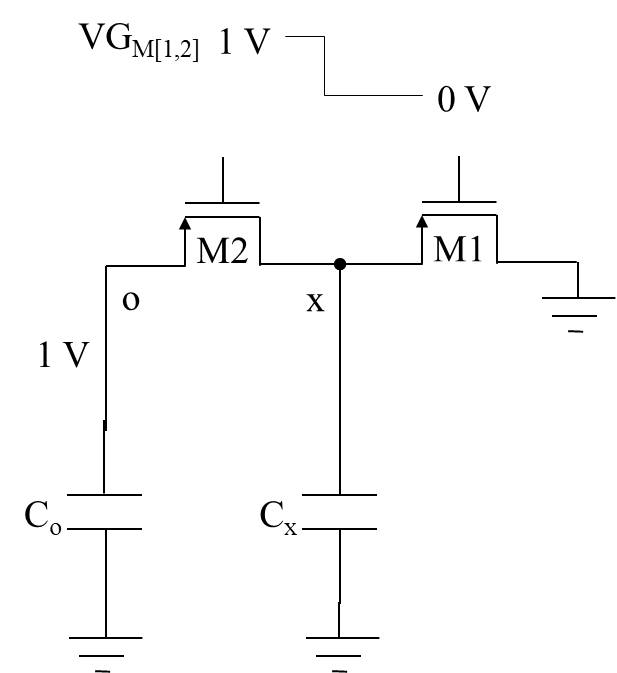

Consider the 2021 Problem 05 about a single stage OR. Let us label the intermediate net between the pulldown PMOSs as net x. Assume that (i) the output c is parked at VCC-VTH from a prior pullup transition and (ii) net x is initialized to 0 V prior to the discharge path (pulldown PMOSs) being enabled.

When the input transitions to logic "0" (0 V), what is the final voltage at net x? (Example answer: V(x) = VTH)

When the input transitions to logic "0" (0 V), what is the final voltage at net x? (Example answer: V(x) = VTH)

■ Reply no later than a couple of days before the end of the month to isaac.abraham@intel.com, Subject “Analog Beat 2022 Problem #”. Last reply of multiple replies will be considered. Earlier replies help with tie-breaks at the end.

The output net is on the left side of the figure, labeled o and shown pre-charged to 1 V from a previous transition where the NMOS pullup(s) were ON.

When M1 and M2 are ON, each will allow charges to pass through, until their respective VSG ≥ VTH. Therefore V(x) will eventually settle to VTH.